# Dive into Deep Learning Compiler Release 0.1

Contributors

Oct 16, 2020

# Contents

| 1 | Getting Started 3                  |                                         |  |  |  |

|---|------------------------------------|-----------------------------------------|--|--|--|

|   | 1.1                                | Installation                            |  |  |  |

|   | 1.2                                | Vector Add                              |  |  |  |

|   | 1.3                                | Neural Network Inference                |  |  |  |

|   | 1.4                                | Running on a Remote Machine             |  |  |  |

| 2 | Expressions for Operators 19       |                                         |  |  |  |

| - | 2.1                                | Data Types         19                   |  |  |  |

|   | 2.2                                | Shapes                                  |  |  |  |

|   | 2.3                                | Index and Shape Expressions             |  |  |  |

|   | 2.4                                | Reduction Operations                    |  |  |  |

|   | 2.5                                | Conditional Expression: if-then-else 29 |  |  |  |

|   | 2.6                                | Truth Value Testing: all and any 30     |  |  |  |

|   |                                    |                                         |  |  |  |

| 3 |                                    | mon Operators 33                        |  |  |  |

|   | 3.1                                | Broadcast Add                           |  |  |  |

|   | 3.2                                | Matrix Multiplication                   |  |  |  |

|   | 3.3                                | Convolution                             |  |  |  |

|   | 3.4                                | Depthwise Convolution                   |  |  |  |

|   | 3.5                                | Pooling                                 |  |  |  |

|   | 3.6                                | Batch Normalization                     |  |  |  |

| 4 | Operator Optimizations on CPUs 57  |                                         |  |  |  |

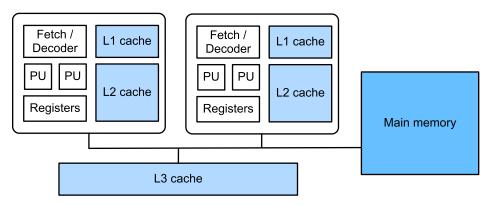

|   | 4.1                                | CPU Architecture                        |  |  |  |

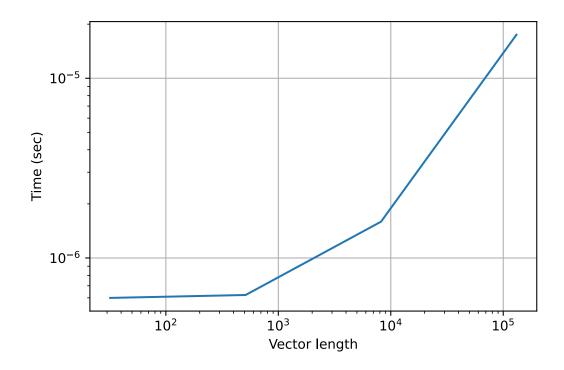

|   | 4.2                                | Function Call Overhead62                |  |  |  |

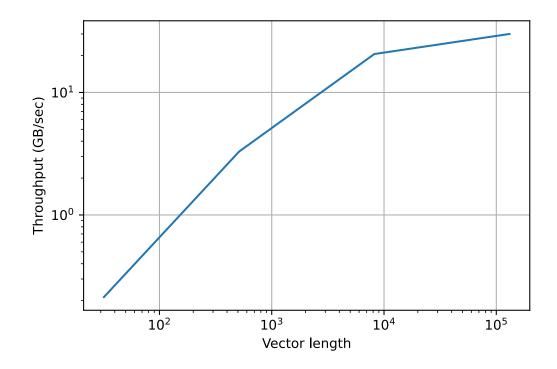

|   | 4.3                                | Vector Add                              |  |  |  |

|   | 4.4                                | Broadcast Add                           |  |  |  |

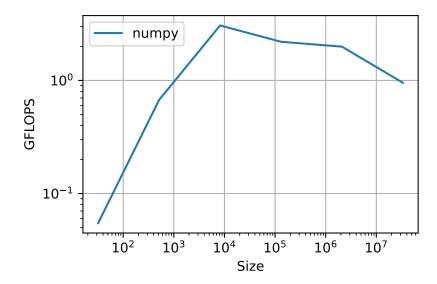

|   | 4.5                                | Matrix Multiplication                   |  |  |  |

|   | 4.6                                | Improve Cache Efficiency by Blocking    |  |  |  |

|   | 4.7                                | Convolution                             |  |  |  |

|   | 4.8                                | Packed Convolution                      |  |  |  |

|   | 4.9                                | Depthwise Convolution                   |  |  |  |

|   | 4.10                               | Pooling                                 |  |  |  |

|   | 4.11                               | Batch Normalization                     |  |  |  |

| 5 | Operator Optimizations on GPUs 115 |                                         |  |  |  |

|   | 5.1                                | GPU Architecture                        |  |  |  |

|   | 5.2                                | Vector Add                              |  |  |  |

|   | 5.3                                | Broadcast Add                           |  |  |  |

|   | 5.4                                | Matrix Multiplication                   |  |  |  |

|   | 5.5                                | Convolution                             |  |  |  |

|     | 5.6          | Depthwise Convolution |     |  |

|-----|--------------|-----------------------|-----|--|

|     | 5.7          | Pooling               |     |  |

|     | 5.8          | Batch Norm            | 49  |  |

| 6   | Neura        | al Networks           | 153 |  |

| 7   | Deployment   |                       |     |  |

| 8   | Discussions  |                       |     |  |

| Bil | Bibliography |                       |     |  |

#### Working in progress. Check our roadmap<sup>1</sup> for more details.

This project is for readers who are interested in high-performance implementation of their programs utilizing deep learning techniques, especially model inference, but may not have got their hands dirty yet. We assume readers have a minimal background of only having experience on NumPy before. With this in mind, we will explain things from scratch and introduce relative background when needed. Experienced readers, however, should also find the contents useful.

We roughly classify contents into three major parts. In the first part, we will introduce how to implement and optimize operators, such as matrix multiplication and convolution, for various hardware platforms. This is the basic component for deep learning as well as scientific computing in general. In the second part, we will show how to convert neural network models from various deep learning frameworks and further optimize them in the program level. The last part we will address how to deploy the optimized program into various environment such as mobile phones. In addition, at the end of the book, we plan to cover some latest advance of the deep learning compiler domain.

<sup>&</sup>lt;sup>1</sup> http://bit.ly/2NQ7gh3

# **1** | Getting Started

Let's start your journey! There's a lot to learn, but every journey starts somewhere. In this part, we'll discuss:

- Installing required libraries so you can run (almost) every chapter by yourself

- Writing an operator that adds two vectors

- · Compiling a neural network model to run the inference, and saving the compiled library

# 1.1 Installation

Each section of this book is a Jupyter notebook. The easiest way to run them is clicking the **COLAB** button on the upper right of the HTML page, which will directly you to Google Colab with the corresponding notebook opened. Running the first code cell will connect to a host runtime and show the following warning message. You can click RUN ANYWAY to continue.

Fig. 1.1.1: Click RUN ANYWAY to run a section on Colab.

The reset of this section will go through how to set up a Python environment, Jupyter's interactive notebooks, the relevant libraries, and the code needed to run the book you can run them on your machines.

## 1.1.1 Obtaining Source Codes

The source code package containing all notebooks is available at http://tvm.d2l.ai/d2l-tvm.zip. Please download it and extract it into a folder. For example, on Linux/macOS, if you have both wget and unzip installed, you can do it through:

```

wget http://tvm.d2l.ai/d2l-tvm.zip

unzip d2l-tvm.zip -d d2l-tvm

```

#### 1.1.2 Installing Running Environment

If you have both Python 3.5 or later and pip installed, the easiest way to install the running environment is through pip. The required packages are

- d2ltvm for all dependencies such as Jupyter and saved code blocks

- tvm (Chen et al., 2018) for the deep learning compiler we are using

- mxnet as the baseline in some chapters

First install d2ltvm:

pip install git+https://github.com/d2l-ai/d2l-tvm

Then compile tvm from source codes. TVM doesn't have a pip package because it highly depends on the libraries available on your system. Please follow the instructions on tvm.ai<sup>2</sup> to install tvm. The configuration in config.cmake this book requires at least

```

set(USE_LLVM ON)

```

If you plan to run on Nvidia GPUs as well, you will also need to

```

set(USE_CUDA ON)

```

Also don't forget to enable cython, which accelerates the performance. You just need to run make cython in the TVM source folder.

If luckily you are using Ubuntu with python-3.7, llvm-6.0 and cuda-10.1 installed, you may use the pre-built library that is for evaluating this book:

Our code runs on tvm-0.7-dev1 for now.

Finally, install MXNet's CUDA version if GPUs are available (Chen et al., 2015). Assume you are have CUDA 10.1 installed, then

```

pip install mxnet-cu101

```

<sup>&</sup>lt;sup>2</sup> https://docs.tvm.ai/install/from\_source.html

You can change the 101 to match your CUDA version.

Once all packages are installed, you can open the Jupyter notebook by

jupyter notebook

At this point open http://localhost:8888 (which usually opens automatically) in the browser, then you can view and run the code in each section of the book.

## 1.1.3 Code

Throughout the book, we save reusable code blocks in the d2ltvm package by adding the comment: "# Save to the d2ltvm package." before the code block. For example, the following code snippet shows the libraries imported by d2ltvm.

```

# Save to the d2ltvm package.

import tvm

from tvm import te

import time

import timeit

import numpy as np

from matplotlib import pyplot as plt

from IPython import display

try:

import mxnet as mx

except:

pass

```

## **1.1.4 Discussions**<sup>3</sup>

# 1.2 Vector Add

Now you have installed all libraries, let's write our first program: summing two n-dimensional vectors a and b. It's straightforward in NumPy, where we can do it by c = a + b.

## 1.2.1 Implementing with NumPy

```

import numpy as np

np.random.seed(0)

n = 100

a = np.random.normal(size=n).astype(np.float32)

b = np.random.normal(size=n).astype(np.float32)

c = a + b

```

Here we create two random vectors with length 100, and sum them element-wisely. Note that NumPy in default uses 64-bit floating-points or 64-bit integers, which is different from 32-bit floating point typically used in deep learning, so we explicitly cast the data type.

<sup>&</sup>lt;sup>3</sup> https://discuss.tvm.ai/t/getting-started-installation/4706

Although we can use the build-in + operator in NumPy to realize element-wise add, let's try to implement it by only using scalar operators. It will help us understand the implementation with TVM. The following function uses a for-loop to iterate over every element of the vectors, and then add two elements together with the scalar + operator each time.

```

def vector_add(a, b, c):

for i in range(n):

c[i] = a[i] + b[i]

d = np.empty(shape=n, dtype=np.float32)

vector_add(a, b, d)

np.testing.assert_array_equal(c, d)

```

Given we will frequently create two random ndarrays and another empty one to store the results in the following chapters, we save this routine to reuse it in the future.

```

# Save to the d2ltvm package.

def get_abc(shape, constructor=None):

"""Return random a, b and empty c with the same shape.

"""

np.random.seed(0)

a = np.random.normal(size=shape).astype(np.float32)

b = np.random.normal(size=shape).astype(np.float32)

c = np.empty_like(a)

if constructor:

a, b, c = [constructor(x) for x in (a, b, c)]

return a, b, c

```

Note that we fixed the random seed so that we will always get the same results to facilitate the comparison between NumPy, TVM and others. In addition, it accepts an optional constructor to convert the data into a different format.

## **1.2.2 Defining the TVM Computation**

Now let's implement vector\_add in TVM. The TVM implementation differs from above in two ways:

- 1. We don't need to write the complete function, but only to specify how each element of the output, i.e. c[i], is computed

- 2. TVM is symbolic, we create symbolic variables by specifying their shapes, and define how the program will be computed

In the following program, we first declare the placeholders A and B for both inputs by specifying their shapes, (n, ), through tvm.te.placeholder. Both A and B are Tensor objects, which we can feed data later. We assign names to them so we can print an easy-to-read program later.

Next we define how the output C is computed by tvm.compute. It accepts two arguments, the output shape, and a function to compute each element by giving its index. Since the output is a vector, its elements are indexed by integers. The lambda function defined in tvm.compute accepts a single argument i, and returns c[i], which is identical to c[i] = a[i] + b[i] defined in vector\_add. One difference is that we don't write the for-loop, which will be filled by TVM later.

```

import tvm

from tvm import te # te stands for tensor expression

# Save to the d2ltvm package.

def vector_add(n):

"""TVM expression for vector add"""

A = te.placeholder((n,), name='a')

B = te.placeholder((n,), name='b')

C = te.compute(A.shape, lambda i: A[i] + B[i], name='c')

return A, B, C

A, B, C = vector_add(n)

type(A), type(C)

```

(tvm.te.tensor.Tensor, tvm.te.tensor.Tensor)

We can see that A, B, and C are all Tensor objects, which can be viewed as a symbolic version of NumPy's ndarray. We can access the variables' attributes such as data type and shape. But those values don't have concrete values right now.

(A.dtype, A.shape), (C.dtype, C.shape)

(('float32', [100]), ('float32', [100]))

The operation that generates the tensor object can be accessed by A. op.

type(A.op), type(C.op)

(tvm.te.tensor.PlaceholderOp, tvm.te.tensor.ComputeOp)

We can see that the types of the operations for A and C are different, but they share the same base class Operation, which represents an operation that generates a tensor object.

```

A.op.__class__._bases__[0]

```

tvm.te.tensor.Operation

#### 1.2.3 Creating a Schedule

To run the computation, we need to specify how to execute the program, for example, the order to access data and how to do multi-threading parallelization. Such an execution plan is called a *schedule*. Since C is the output tensor, let's create a default schedule on its operator and print the pseudo codes.

s = te.create\_schedule(C.op)

A schedule consists of several stages. Each stage corresponds to an operation to describe how it is scheduled. We can access a particular stage by either s[C] or s[C.op].

```

type(s), type(s[C])

```

(tvm.te.schedule.Schedule, tvm.te.schedule.Stage)

Later on we will see how to change the execution plan to better utilize the hardware resources to improve its efficiency. Here let's see the default execution plan by printing the C-like pseudo codes.

```

tvm.lower(s, [A, B, C], simple_mode=True)

```

```

produce c {

for (i, 0, 100) {

c[i] = (a[i] + b[i])

}

}

```

The lower method accepts the schedule and input and output tensors. The simple\_mode=True will print the program in a simple and compact way. Note that the program has added proper for-loops according to the output shape. Overall, it's quite similar to the preview function vector\_add.

Now you see that TVM separates the computation and the schedule. The computation defines how the results are computed, which will not change no matter on what hardware platform you run the program. On the other hand, an efficient schedule are often hardware dependent, but changing a schedule will not impact the correctness. The idea of separating computation from schedule is inherited by TVM from Halide (Ragan-Kelley et al., 2013).

#### **1.2.4 Compilation and Execution**

Once both computation and schedule are defined, we can compile them into an executable module with tvm. build. It accepts the same argument as tvm.lower. In fact, it first calls tvm.lower to generate the program and then compiles to machine codes.

```

mod = tvm.build(s, [A, B, C])

type(mod)

```

```

tvm.runtime.module.Module

```

It returns an executable module object. Now we can feed data for A, B and C to run it. The tensor data must be tvm.ndarray.NDArray object. The easiest way is to create NumPy ndarray objects first and then convert them into TVM ndarray by tvm.nd.array. We can convert them back to NumPy by the asnumpy method.

```

x = np.ones(2)

y = tvm.nd.array(x)

type(y), y.asnumpy()

```

```

(tvm.runtime.ndarray.NDArray, array([1., 1.]))

```

Now let's construct data and return them as TVM ndarrays.

a, b, c = get\_abc(100, tvm.nd.array)

Do the computation, and verify the results.

```

mod(a, b, c)

np.testing.assert_array_equal(a.asnumpy() + b.asnumpy(), c.asnumpy())

```

#### 1.2.5 Argument Constraints

Remember that we specified both inputs to be 100-length vectors when declaring A and B.

```

A.shape, B.shape, C.shape

```

```

([100], [100], [100])

```

TVM will check if the input shapes satisfy this specification.

```

try:

a, b, c = get_abc(200, tvm.nd.array)

mod(a, b, c)

except tvm.TVMError as e:

print(e)

```

```

Traceback (most recent call last):

[bt] (1) /var/lib/jenkins/miniconda3/envs/d2l-tvm-0/lib/python3.7/site-

packages/tvm/libtvm.so(TVMFuncCall+0x61) [0x7f8eec7a60f1]

[bt] (0) /var/lib/jenkins/miniconda3/envs/d2l-tvm-0/lib/python3.7/site-

packages/tvm/libtvm.so(+0xcab5a1) [0x7f8eec78d5a1]

File "/home/ubuntu/tvm/src/runtime/library_module.cc", line 89

TVMError: Check failed: ret == 0 (-1 vs. 0) : Assert fail: (100 == int32(arg0.

shape[0])), Argument arg0.shape[0] has an unsatisfied constraint

```

The default data type in TVM is float 32.

A.dtype, B.dtype, C.dtype

('float32', 'float32', 'float32')

An error will appear if input with a different data type.

```

try:

a, b, c = get_abc(100, tvm.nd.array)

a = tvm.nd.array(a.asnumpy().astype('float64'))

mod(a, b, c)

except tvm.TVMError as e:

print(e)

```

#### 1.2.6 Saving and Loading a Module

A compiled a module can be saved into disk,

```

mod_fname = 'vector-add.tar'

mod.export_library(mod_fname)

```

#### and then loaded back later.

loaded\_mod = tvm.runtime.load\_module(mod\_fname)

#### Verify the results.

```

a, b, c = get_abc(100, tvm.nd.array)

loaded_mod(a, b, c)

np.testing.assert_array_equal(a.asnumpy() + b.asnumpy(), c.asnumpy())

```

#### 1.2.7 Summary

Implementing an operator using TVM has three steps:

- 1. Declare the computation by specifying input and output shapes and how each output element is computed.

- 2. Create a schedule to (hopefully) fully utilize the machine resources.

- 3. Compile to the hardware target.

In addition, we can save the compiled module into disk so we can load it back later.

#### **1.2.8 Discussions**<sup>4</sup>

# **1.3 Neural Network Inference**

You have seen how to implement and compile a simple vector addition operator in Section 1.2. Now we will make a big jump to compile a whole pre-trained neural network, which consists of a set of operators, to run the inference.

<sup>&</sup>lt;sup>4</sup> https://discuss.tvm.ai/t/getting-started-vector-addition/4707

import numpy as np import mxnet as mx from PIL import Image import tvm from tvm import relay

Here three additional modules are imported compared to the previous chapter. We will use PIL to read images, mxnet to obtain pre-trained neural networks, and the relay module (Roesch et al., 2019) in TVM to convert and optimize a neural network. Relay is the high-level intermediate representation (IR) in TVM to represent a neural network.

#### 1.3.1 Obtaining Pre-trained Models

A pre-trained model means a neural network with parameters trained on a data set. Here we download and load a ResNet-18 model by specifying pretrained=True from MXNet's model zoo (Chen et al., 2015). If you want to know details about this model, please refer to Chapter 7.6 in  $D2L^5$ . You can find more models on the MXNet model zoo<sup>6</sup> page, or refer to GluonCV<sup>7</sup> and GluonNLP<sup>8</sup> for more computer vision and natural language models.

```

model = mx.gluon.model_zoo.vision.resnet18_v2(pretrained=True)

len(model.features), model.output

```

```

(13, Dense(512 -> 1000, linear))

```

The loaded model is trained on the Imagenet 1K dataset, which contains around 1 million natural object images among 1000 classes. The model has two parts, the main body part model.features contains 13 blocks, and the output layer is a dense layer with 1000 outputs.

The following code block loads the text labels for each class in the Imagenet dataset.

```

with open('../data/imagenet1k_labels.txt') as f:

labels = eval(f.read())

```

## 1.3.2 Pre-processing Data

We first read a sample image. It is resized to the size, i.e. 224 px width and height, which we used to train the neural network.

```

image = Image.open('../data/cat.jpg').resize((224, 224))

image

```

<sup>&</sup>lt;sup>5</sup> http://d2l.ai/chapter\_convolutional-modern/resnet.html

<sup>&</sup>lt;sup>6</sup> https://mxnet.apache.org/api/python/docs/api/gluon/model\_zoo/index.html

<sup>&</sup>lt;sup>7</sup> https://gluon-cv.mxnet.io/model\_zoo/index.html

<sup>&</sup>lt;sup>8</sup> http://gluon-nlp.mxnet.io/model\_zoo/index.html

According to the model zoo page<sup>9</sup>. Image pixels are normalized on each color channel, and the data layout is (batch, RGB channels, height, width). The following function transforms the input image to satisfy the requirement.

```

# Save to the d2ltvm package

def image_preprocessing(image):

image = np.array(image) - np.array([123., 117., 104.])

image /= np.array([58.395, 57.12, 57.375])

image = image.transpose((2, 0, 1))

image = image[np.newaxis, :]

return image.astype('float32')

x = image_preprocessing(image)

x.shape

```

(1, 3, 224, 224)

#### **1.3.3 Compile Pre-trained Models**

To compile a model, we first express the MXNet model in Relay IR, which the from\_mxnet method could help. In the method, we provide the model with the input data shape. Some neural networks may require some dimension(s) of the data shape to be determined later. However, in ResNet model the data shape is fixed, which makes it easier for the compiler to achieve high performance. We will mostly stick to fixed data shape in the book. We only touch the dynamic data shape (i.e. some dimension(s) to be determined in runtime) in very late chapters.

```

relay_mod, relay_params = relay.frontend.from_mxnet(model, {'data': x.shape})

type(relay_mod), type(relay_params)

```

<sup>&</sup>lt;sup>9</sup> https://mxnet.apache.org/api/python/docs/api/gluon/model\_zoo/index.html

This method will return the program relay\_mod, which is a relay module, and a dictionary of parameters relay\_params that maps a string key to a TVM ndarray. Next, we lower the module to some lower-level IR which can be consumed by llvm backend. LLVM<sup>10</sup> defines an IR that has been adopted by multiple programming languages. The LLVM compiler is then able to compile the generated programs into machine codes for CPUs. We have already used it to compile the vector addition operator in Section 1.2, despite that we didn't explicitly specify it.

In addition, we set the optimization level to the highest level 3. You may get warning messages that not every operator is well optimized, you can ignore it for now. We will get back to it later.

The compiled module has three parts: graph is a json string described the neural network, mod is a library that contains all compiled operators used to run the inference, and params is a dictionary mapping parameter name to weights.

```

type(graph), type(mod), type(params)

```

(str, tvm.runtime.module.Module, dict)

You can view mod as a TVM module we already seen in Section 1.2.

#### 1.3.4 Inference

Now we can create a runtime to run the model inference, namely the forward pass of a neural network. Creating the runtime needs the neural network definition in json (i.e. graph) and the library that contains machine code of compiled operators (i.e. mod), with a device context that can be constructed from the target. The device is CPU here, specified by llvm. Next we load the parameters with set\_input and run the workload by feeding the input data. Since this network has a single output layer, we can obtain it, a (1, 1000) shape matrix, by get\_output(0). The final output is a 1000-length NumPy vector.

```

ctx = tvm.context(target)

rt = tvm.contrib.graph_runtime.create(graph, mod, ctx)

rt.set_input(**params)

rt.run(data=tvm.nd.array(x))

scores = rt.get_output(0).asnumpy()[0]

scores.shape

```

<sup>&</sup>lt;sup>10</sup> https://en.wikipedia.org/wiki/LLVM

(1000,)

The vector contains the predicted confidence score for each class. Note that the pre-trained model doesn't have the softmax<sup>11</sup> operator, so these scores are not mapped into probabilities in (0, 1). Now we can find the two largest scores and report their labels.

```

a = np.argsort(scores)[-1:-5:-1]

labels[a[0]], labels[a[1]]

```

```

('tiger cat', 'Egyptian cat')

```

## 1.3.5 Saving the Compiled Library

We can save the output of relay.build in disk to reuse them later. The following code block saves the json string, library, and parameters.

```

!rm -rf resnet18*

name = 'resnet18'

graph_fn, mod_fn, params_fn = [name+ext for ext in ('.json','.tar','.params')]

mod.export_library(mod_fn)

with open(graph_fn, 'w') as f:

f.write(graph)

with open(params_fn, 'wb') as f:

f.write(relay.save_param_dict(params))

!ls -alht resnet18*

-rw-r--r-- 1 jenkins jenkins 45M Oct 13 10:45 resnet18.params

-rw-r--r-- 1 jenkins jenkins 28K Oct 13 10:45 resnet18.json

-rw-r--r-- 1 jenkins jenkins 157K Oct 13 10:45 resnet18.tar

```

Now we load the saved module back.

```

loaded_graph = open(graph_fn).read()

loaded_mod = tvm.runtime.load_module(mod_fn)

loaded_params = open(params_fn, "rb").read()

```

And then construct the runtime as before to verify the results

```

loaded_rt = tvm.contrib.graph_runtime.create(loaded_graph, loaded_mod, ctx)

loaded_rt.load_params(loaded_params)

loaded_rt.run(data=tvm.nd.array(x))

loaded_scores = loaded_rt.get_output(0).asnumpy()[0]

tvm.testing.assert_allclose(loaded_scores, scores)

```

<sup>11</sup> https://en.wikipedia.org/wiki/Softmax\_function

#### 1.3.6 Summary

- We can use relay of TVM to convert and compile a neural network into a module for model inference.

- We can save the compiled module into disk to facilitate future deployment.

#### **1.3.7 Discussions**<sup>12</sup>

## 1.4 Running on a Remote Machine

In this book, we will run and optimize programs on various hardware platforms. One way is to log into the machine with the desired hardware, install required packages and then run the workloads there. It, however, makes maintaining the source codes and data difficult, especially when the targeting hardware is with minimal power. In this section, we will describe another solution: running a daemon on the remote machine and then sending the compiled module and input data to it only for execution.

```

import d2ltvm

import numpy as np

import mxnet as mx

import tvm

from tvm import te, rpc, relay

from PIL import Image

```

Note that we imported the rpc module from TVM.  $RPC^{13}$ , namely remote procedure call, enables executing a program on a remote place.

#### 1.4.1 Setup the Remote Machine

We first need to install TVM runtime module on the remote machine. The installation setup is almost identical to TVM (refer to Section 1.1), except that we only need to build the runtime, i.e. make runtime, instead of the whole TVM library. The runtime size is often less than 1MB, which makes it suitable for device with memory constraints. You also need to enable the proper backend, e.g. CUDA or OpenCL, if necessary.

Once the runtime is installed, we can start the daemon by running the following command on the remote machine.

python -m tvm.exec.rpc\_server --host 0.0.0.0 --port=9090

It will start an RPC server which binds the local 9090 port to listen. You should see the following output indicating the server has already started.

INFO:RPCServer:bind to 0.0.0.0:9090

In addition, you need to check two things on the remote machine.

One is the remote machine's IP. On Linux or macOS, you can get it by ifconfig | grep inet. Also remember to open the 9090 port if there is a firewall.

The other one is the target architecture. It's straightforward for GPUs, we will cover it later. For CPUs, the easiest way is installing LLVM on the remote machine and then checking <code>llvm-config --host-target</code>. The return of the remote machine we are using is <code>x86\_64-pc-linux-gnu</code>.

<sup>&</sup>lt;sup>12</sup> https://discuss.tvm.ai/t/getting-started-neural-network-inference/4708

<sup>&</sup>lt;sup>13</sup> https://en.wikipedia.org/wiki/Remote\_procedure\_call

This target triplet has the general format <arch><sub>-<vendor>-<sys>-<abi>, where

- arch: x86, x86\_64, arm, thumb, mips, etc.

- sub: for ARM, there are v5, v6m, v7a, v7m, v8, etc.

- vendor: pc, apple, nvidia, ibm, etc.

- sys: linux, win32, darwin, cuda, none, unknown, etc.

- abi: eabi, gnu, android, macho, elf, etc.

For example, it's x86\_64-apple-darwin17.7.0 for the MacbookPro I'm using, and armv6k-unknown-linux-gnueabihf for the Raspberry Pi 4B.

#### 1.4.2 Compile the Program for the Remote Machine

Let's run the vector addition defined Section 1.2 on the remote machine. Note that we specified the remote machine target through the -target argument for LLVM.

```

n = 100

target = 'llvm -target=x86_64-pc-linux-gnu'

args = d2ltvm.vector_add(n)

s = te.create_schedule(args[-1].op)

mod = tvm.build(s, args, target)

```

Then we save the compiled module to disk, which will be uploaded to the remote machine later.

```

mod_fname = 'vector-add.tar'

mod.export_library(mod_fname)

```

#### 1.4.3 Evaluate on the Remote Machine

We first connect to the remote machine with the IP we checked before.

```

remote = rpc.connect('172.31.0.149', 9090)

```

Next, we send the compiled library to the machine and load it into the memory of the remote machine.

```

remote.upload(mod_fname)

remote_mod = remote.load_module(mod_fname)

```

When creating the data, we specify the device context as CPU on the remote machine. The data will be created on the local machine as before, but will be sent to the remote machine later. Note that we used NumPy to create the data, but there is no need to have the remote machine also installed NumPy.

```

ctx = remote.cpu()

a, b, c = d2ltvm.get_abc(n, lambda x: tvm.nd.array(x, ctx=ctx))

```

Since both data and library are ready on the remote machine, let's execute the program on it as well.

remote\_mod(a, b, c)

Finally, the .asnumpy() method will send the data back to the local machine and convert to a NumPy array. So we can verify the results as before.

```

np.testing.assert_equal(a.asnumpy()+b.asnumpy(), c.asnumpy())

```

#### 1.4.4 Running Neural Network Inference

Let's run the ResNet-18 used in Section 1.3 on the remote machine. As before, we load a sample image and Imagenet 1K labels.

```

image = Image.open('../data/cat.jpg').resize((224, 224))

x = d2ltvm.image_preprocessing(image)

with open('../data/imagenet1k_labels.txt') as f:

labels = eval(f.read())

```

Then we convert, compile and save the module. Note that we just need to save the shared library which contains the machine code of the compiled operators to the disk.

```

mod_fname = 'resnet18.tar'

model = mx.gluon.model_zoo.vision.resnet18_v2(pretrained=True)

relay_mod, relay_params = relay.frontend.from_mxnet(model, {'data': x.shape})

with relay.build_config(opt_level=3):

graph, mod, params = relay.build(relay_mod, target, params=relay_params)

mod.export_library(mod_fname)

```

```

Cannot find config for target=llvm -target=x86_64-pc-linux-gnu, workload=(

→'dense_nopack.x86', ('TENSOR', (1, 512), 'float32'), ('TENSOR', (1000, 512),

→ 'float32'), None, 'float32'). A fallback configuration is used, which may_

→bring great performance regression.

```

Next, we upload the saved library to the remote machine and load it into memory. Then we can create a runtime using the model definition, the remote library and the remote context.

```

remote.upload(mod_fname)

remote_mod = remote.load_module(mod_fname)

remote_rt = tvm.contrib.graph_runtime.create(graph, remote_mod, ctx)

```

The inference is identical to Section 1.3, where both parameters and input are on the local machine. The runtime will upload them into the remote machine properly.

```

remote_rt.set_input(**params)

remote_rt.run(data=tvm.nd.array(x))

scores = remote_rt.get_output(0).asnumpy()[0]

scores.shape

a = np.argsort(scores)[-1:-5:-1]

labels[a[0]], labels[a[1]]

```

## 1.4.5 Summary

- We can install a TVM runtime on a remote machine to start an RPC server to accept workloads to run.

- A program can be compiled locally with specifying the remote machine's architecture target (called cross-compilation), and then run on the remote machine via RPC.

## **1.4.6 Discussions**<sup>14</sup>

<sup>&</sup>lt;sup>14</sup> https://discuss.tvm.ai/t/getting-started-running-on-a-remote-machine/4709

# **2** | Expressions for Operators

We start from operators. As you may know, operators are the building blocks of neural network models. A deep neural network can be expressed as a Directed Acyclic Graph (DAG), which consists of nodes being the operators and edges being the data dependency between nodes. Being able to execute the operators efficiently is of course a necessity to high-performance neural network model execution.

In Section 1.2 you have seen how to build the vector addition expression in TVM. This chapter covers more concepts in TVM to construct expressions. Specifically, you'll learn about data types, shapes, indexing, reduction and control flow, based on which you'll be able to construct operators in the next chapter.

# 2.1 Data Types

Every tensor has a data type, which is typically float32 in deep learning, but also could be int8 (e.g. for model quantization) and others. The tvm\_vector\_add module we created in Section 1.2 only accepts float32 tensors. Let's extend it to other data types in this section.

#### 2.1.1 Specifying a Data Type

To use a data type different to the default float 32, we can specify it explicitly when creating the placeholders. In the following code block, we generalize the vector addition expression defined in Section 1.2 to accept an argument dtype to specify the data type. In particular, we pass dtype to te.placeholder when creating A and B. The result C then obtains the same data type as A and B.

```

import tvm

from tvm import te

import d2ltvm

import numpy as np

n = 100

def tvm_vector_add(dtype):

A = te.placeholder((n,), dtype=dtype)

B = te.placeholder((n,), dtype=dtype)

C = te.compute(A.shape, lambda i: A[i] + B[i])

print('expression dtype:', A.dtype, B.dtype, C.dtype)

s = te.create_schedule(C.op)

return tvm.build(s, [A, B, C])

```

Let's compile a module that accepts int 32 tensors.

mod = tvm\_vector\_add('int32')

expression dtype: int32 int32 int32

Then we define a method to verify the results with a particular data type. Note that we pass a constructor that modifies the tensor data type by astype.

```

def test_mod(mod, dtype):

a, b, c = d2ltvm.get_abc(n, lambda x: tvm.nd.array(x.astype(dtype)))

print('tensor dtype:', a.dtype, b.dtype, c.dtype)

mod(a, b, c)

np.testing.assert_equal(c.asnumpy(), a.asnumpy() + b.asnumpy())

test_mod(mod, 'int32')

```

tensor dtype: int32 int32 int32

Let's try other data types as well

```

for dtype in ['float16', 'float64', 'int8','int16', 'int64']:

mod = tvm_vector_add(dtype)

test_mod(mod, dtype)

```

```

expression dtype: float16 float16 float16

tensor dtype: float16 float16 float16

expression dtype: float64 float64 float64

tensor dtype: float64 float64 float64

expression dtype: int8 int8 int8

tensor dtype: int16 int16 int16

tensor dtype: int16 int16 int16

tensor dtype: int64 int64 int64

tensor dtype: int64 int64

```

#### 2.1.2 Converting Elements Data Types

Besides constructing a tensor with a particular data type, we can also cast the data type of a tensor element during the computation. The following method is the same as  $tvm\_vector\_add$  except that it casts the data type of A and B in te.compute, leaving the data type defined in te.placeholder as default (float32). Because of the casting done by astype, the result C will have the data type specified by dtype.

Then we define a similar test function to verify the results.

```

def test_mod_2(mod, dtype):

a, b, c = d2ltvm.get_abc(n)

# by default `get_abc` returns NumPy ndarray in float32

a_tvm, b_tvm = tvm.nd.array(a), tvm.nd.array(b)

c_tvm = tvm.nd.array(c.astype(dtype))

print('tensor dtype:', a_tvm.dtype, b_tvm.dtype, c_tvm.dtype)

mod(a_tvm, b_tvm, c_tvm)

np.testing.assert_equal(c_tvm.asnumpy(), a.astype(dtype) + b.

↔astype(dtype))

mod = tvm_vector_add_2('int32')

test_mod_2(mod, 'int32')

```

expression dtype: float32 float32 int32 tensor dtype: float32 float32 int32

#### 2.1.3 Summary

- We can specify the data type by dtype when creating TVM placeholders.

- The data type of a tensor element can be cast by astype in TVM compute.

## 2.2 Shapes

The vector addition module defined in Section 1.2 only accepts vectors with 100-length. It's too restrictive for real scenarios where inputs can have arbitrary shapes. In this section, we will show how to relax this constraint to deal with general cases.

#### 2.2.1 Variable Shapes

Remember that we create symbolic placeholders for tensors A and B so we can feed with data later. We can do the same thing for the shape as well. In particular, the following code block uses te.var to create a symbolic variable for an int32 scalar, whose value can be specified later.

```

import d2ltvm

import numpy as np

import tvm

from tvm import te

n = te.var(name='n')

type(n), n.dtype

```

```

(tvm.tir.expr.Var, 'int32')

```

Now we can use (n, ) to create a placeholder for an arbitrary length vector.

```

A = te.placeholder((n,), name='a')

B = te.placeholder((n,), name='b')

C = te.compute(A.shape, lambda i: A[i] + B[i], name='c')

s = te.create_schedule(C.op)

tvm.lower(s, [A, B, C], simple_mode=True)

produce c {

for (i, 0, n) {

c[(i*stride)] = (a[(i*stride)] + b[(i*stride)])

}

```

Compared to the generated pseudo codes in Section 1.2, we can see the upper bound value of the for loop is changed from 100 to n.

Now we define a similar test function as before to verify that the compiled module is able to correctly execute on input vectors with different lengths.

```

def test_mod(mod, n):

a, b, c = d2ltvm.get_abc(n, tvm.nd.array)

mod(a, b, c)

print('c.shape:', c.shape)

np.testing.assert_equal(c.asnumpy(), a.asnumpy() + b.asnumpy()))

mod = tvm.build(s, [A, B, C])

test_mod(mod, 5)

test_mod(mod, 5)

test_mod(mod, 1000)

c.shape: (5,)

c.shape: (1000,)

```

But note that we still place the constraint that A, B, and C must be in the same shape. So an error will occur if it is not satisfied.

#### 2.2.2 Multi-dimensional Shapes

You may already notice that a shape is presented as a tuple. A single element tuple means a 1-D tensor, or a vector. We can extend it to multi-dimensional tensors by adding variables to the shape tuple.

The following method builds a module for multi-dimensional tensor addition, the number of dimensions is specified by ndim. For a 2-D tensor, we can access its element by A[i,j], similarly A[i,j,k] for 3-D tensors. Note that we use \*i to handle the general multi-dimensional case in the following code.

```

def tvm_vector_add(ndim):

A = te.placeholder([te.var() for _ in range(ndim)])

B = te.placeholder(A.shape)

C = te.compute(A.shape, lambda *i: A[i] + B[i])

s = te.create_schedule(C.op)

return tvm.build(s, [A, B, C])

```

Verify that it works beyond vectors.

}

```

mod = tvm_vector_add(2)

test_mod(mod, (2, 2))

mod = tvm_vector_add(4)

test_mod(mod, (2, 3, 4, 5))

c.shape: (2, 2)

```

```

c.shape: (2, 3, 4, 5)

```

#### 2.2.3 Summary

- We can use te.var() to specify the dimension(s) of a shape when we don't know the concrete data shape before execution.

- The shape of an *n*-dimensional tensor is presented as an *n*-length tuple.

# 2.3 Index and Shape Expressions

You already know that a shape can be a tuple of symbols such as (n, m) and the elements can be accessed via indexing, e.g. a[i, j]. In practice, both shapes and indices may be computed through complex expressions. We will go through several examples in this section.

```

import d2ltvm

import numpy as np

import tvm

from tvm import te

```

#### 2.3.1 Matrix Transpose

Our first example is matrix transpose a.T, in which we access a's elements by columns.

```

n = te.var('n')

m = te.var('m')

A = te.placeholder((n, m), name='a')

B = te.compute((m, n), lambda i, j: A[j, i], 'b')

s = te.create_schedule(B.op)

tvm.lower(s, [A, B], simple_mode=True)

```

```

produce b {

for (i, 0, m) {

for (j, 0, n) {

b[((i*stride) + (j*stride))] = a[((j*stride) + (i*stride))]

}

}

}

```

Note that the 2-D index, e.g. b[i, j] are collapsed to the 1-D index b[((i\*n) + j)] to follow the C convention.

Now verify the results.

```

a = np.arange(12, dtype='float32').reshape((3, 4))

b = np.empty((4, 3), dtype='float32')

a, b = tvm.nd.array(a), tvm.nd.array(b)

mod = tvm.build(s, [A, B])

mod(a, b)

print(a)

print(b)

```

```

[[ 0. 1. 2. 3.]

[ 4. 5. 6. 7.]

[ 8. 9. 10. 11.]]

[[ 0. 4. 8.]

[ 1. 5. 9.]

[ 2. 6. 10.]

[ 3. 7. 11.]]

```

### 2.3.2 Reshaping

Next let's use expressions for indexing. The following code block reshapes a 2-D array a (n by m as defined above) to 1-D (just like a.reshape(-1) in NumPy). Note how we convert the 1-D index i to the 2-D index [i//m, i%m].

```

B = te.compute((m*n, ), lambda i: A[i//m, i%m], name='b')

s = te.create_schedule(B.op)

tvm.lower(s, [A, B], simple_mode=True)

produce b {

for (i, 0, (m*n)) {

b[i] = a[((floordiv(i, m)*stride) + (floormod(i, m)*stride))]

}

}

```

Since an *n*-D array is essentially listed in the memory as a 1-D array, the generated code does not rearrange the data sequence, but it simplifies the index expression from 2-D ((i//m) \*m + i%m) to 1-D (i) to improve the efficiency.

We can implement a general 2-D reshape function as well.

(continues on next page)

} } }

When testing the results, we should be aware that we put no constraint on the output shape, which can have an arbitrary shape (p, q), and therefore TVM will not be able to check if qp = nm for us. For example, in the following example we created a b with size (20) larger than a (12), then only the first 12 elements in b are from a, others are uninitialized values.

```

mod = tvm.build(s, [A, B])

a = np.arange(12, dtype='float32').reshape((3,4))

b = np.zeros((5, 4), dtype='float32')

a, b = tvm.nd.array(a), tvm.nd.array(b)

mod(a, b)

print(b)

[[0.00000e+00 1.00000e+00 2.00000e+00 3.00000e+00]

```

```

[4.000000e+00 5.000000e+00 6.000000e+00 7.000000e+00]

[8.000000e+00 9.000000e+00 1.000000e+01 1.100000e+01]

[8.722636e-23 3.066461e-41 9.108440e-44 0.0000000e+00]

[8.743578e-23 3.066461e-41 8.741932e-23 3.066461e-41]]

```

#### 2.3.3 Slicing

Now let's consider a special slicing operator a [bi::si, bj::sj] where bi, bj, si and sj can be specified later. Now the output shape needs to be computed based on the arguments. In addition, we need to pass the variables bi, bj, si and sj as arguments when compiling the module.

```

bi, bj, si, sj = [te.var(name) for name in ['bi', 'bj', 'si', 'sj']]

B = te.compute(((n-bi)//si, (m-bj)//sj), lambda i, j: A[i*si+bi, j*sj+bj],_

→name='b')

s = te.create_schedule(B.op)

mod = tvm.build(s, [A, B, bi, si, bj, sj])

```

Now test two cases to verify the correctness.

```

b = tvm.nd.array(np.empty((1, 3), dtype='float32'))

mod(a, b, 1, 2, 1, 1)

np.testing.assert_equal(b.asnumpy(), a.asnumpy()[1::2, 1::1])

b = tvm.nd.array(np.empty((1, 2), dtype='float32'))

mod(a, b, 2, 1, 0, 2)

np.testing.assert_equal(b.asnumpy(), a.asnumpy()[2::1, 0::2])

```

#### 2.3.4 Summary

- Both shape dimensions and indices can be expressions with variables.

- If a variable doesn't only appear in the shape tuple, we need to pass it as an argument when compiling.

# 2.4 Reduction Operations

Reduction is an operation to reduce certain dimension(s) of an input tensor, usually to scalar(s), e.g. np.sum in NumPy. Reduction is often straightforward to implement with for-loops. But it's a little bit more complicated in TVM since we cannot use a Python for-loop directly. In this section, we will describe how to implement reduction in TVM.

```

import d2ltvm

import numpy as np

import tvm

from tvm import te

```

#### 2.4.1 Sum

Let's start with summing the rows of a 2-D matrix to reduce it to be a 1-D vector. In NumPy, we can do it with the sum method.

```

a = np.random.normal(size=(3,4)).astype('float32')

a.sum(axis=1)

```

array([ 1.8948135, -2.4319794, 1.9638997], dtype=float32)

As we did before, let's implement this operation from scratch to help understand the TVM expression.

```

def sum_rows(a, b):

"""a is an n-by-m 2-D matrix, b is an n-length 1-D vector

"""

n = len(b)

for i in range(n):

b[i] = np.sum(a[i,:])

b = np.empty((3,), dtype='float32')

sum_rows(a, b)

b

```

array([ 1.8948135, -2.4319794, 1.9638997], dtype=float32)

It's fairly straightforward, we first iterate on the first dimension, axis=0, and then sum all elements on the second dimension to write the results. In NumPy, we can use : to slice all elements along that dimension.

Now let's implement the same thing in TVM. Comparing to the vector addition in Section 1.2, we used two new operators here. One is tvm.reduce\_axis, which create an axis for reduction with range from 0 to m. It's functionally similar to the : used in sum\_rows, but we need to explicitly specify the range in TVM. The other one is tvm.sum, which sums all elements along the reducing axis k and returns a scalar.

```

b[(i*stride)] = 0f

for (j, 0, m) {

b[(i*stride)] = (b[(i*stride)] + a[((i*stride) + (j*stride))])

}

}

```

We can see that the generated pseudo codes expand tvm. sum into another for loop along axis k. As mentioned before, the pseudo codes are C-like, so the index of a [i, j] is expanded to (i\*m)+j by treating a as a 1-D array. Also note that b is initialized to be all-zero before summation.

Now test the results are as expected.

```

mod = tvm.build(s, [A, B])

c = tvm.nd.array(np.empty((3,), dtype='float32'))

mod(tvm.nd.array(a), c)

np.testing.assert_equal(b, c.asnumpy())

```

We know that a.sum() will sum all elements in a and returns a scalar. Let's also implement this in TVM. To do it, we need another reduction axis along the first dimension, whose size is n. The result is a scalar, namely a 0-rank tensor, can be created with an empty tuple ().

```

i = te.reduce_axis((0, n), name='i')

B = te.compute((), lambda: te.sum(A[i, j], axis=(i, j)), name='b')

s = te.create_schedule(B.op)

tvm.lower(s, [A, B], simple_mode=True)

```

```

produce b {

b[0] = 0f

for (i, 0, n) {

for (j, 0, m) {

b[0] = (b[0] + a[((i*stride) + (j*stride))])

}

}

}

```

Let's also verify the results.

```

mod = tvm.build(s, [A, B])

c = tvm.nd.array(np.empty((), dtype='float32'))

mod(tvm.nd.array(a), c)

np.testing.assert_allclose(a.sum(), c.asnumpy(), atol=1e-5)

```

In this case we use <code>np.testing.assert\_allclose</code> instead of <code>np.testing.assert\_equal</code> to

verify the results as the calculation on float 32 numbers may differ due to the numerical error.

Beyond tvm.sum, there are other reduction operators in TVM such as tvm.min and tvm.max. We can also use them to implement the corresponding reduction operations as well.

#### 2.4.2 Commutative Reduction

In mathematics, an operator  $\circ$  is commutative if  $a \circ b = b \circ a$ . TVM allows to define a customized commutative reduction operator through twm.comm\_reducer. It accepts two function arguments, one defines how to compute  $a \circ b$ , the other one specifies the initial value.

Let's use the production by rows, e.g a.prod(axis=1), as an example. Again, we first show how to implement it from scratch.

```

def prod_rows(a, b):

"""a is an n-by-m 2-D matrix, b is an n-length 1-D vector

"""

n, m = a.shape

for i in range(n):

b[i] = 1

for j in range(m):

b[i] = b[i] * a[i, j]

```

As can be seen, we need to first initialize the return values to be 1, and then compute the reduction using scalar product \*. Now let's define these two functions in TVM to serve as the arguments of te.comm\_reducer. As discussed, the first one defines  $a \circ b$  with two scalar inputs. The second one accepts a data type argument to return the initial value of an element. Then we can create the reduction operator.

```

comp = lambda a, b: a * b

init = lambda dtype: tvm.tir.const(1, dtype=dtype)

product = te.comm_reducer(comp, init)

```

The usage of product is similar to te.sum. Actually, te.sum is a pre-defined reduction operator using the same way.

```

n = te.var('n')

m = te.var('m')

A = te.placeholder((n, m), name='a')

k = te.reduce_axis((0, m), name='k')

B = te.compute((n,), lambda i: product(A[i, k], axis=k), name='b')

s = te.create_schedule(B.op)

tvm.lower(s, [A, B], simple_mode=True)

```

```

produce b {

for (i, 0, n) {

b[(i*stride)] = 1f

for (k, 0, m) {

b[(i*stride)] = (b[(i*stride)]*a[((i*stride) + (k*stride))])

}

}

}

```

The generated pseudo codes are similar to the one for summing by rows, except for the initialized value and the reduction arithmetic.

Again, let's verify the results.

```

mod = tvm.build(s, [A, B])

b = tvm.nd.array(np.empty((3,), dtype='float32'))

mod(tvm.nd.array(a), b)

np.testing.assert_allclose(a.prod(axis=1), b.asnumpy(), atol=1e-5)

```

#### 2.4.3 Summary

- We can apply a reduction operator, e.g. te.sum over a reduction axis te.reduce\_axis.

- We can implement customized commutative reduction operators by te.comm\_reducer.

## 2.5 Conditional Expression: if-then-else

The if-then-else statement is supported through te.if\_then\_else. In this section, we will introduce this expression using computing the lower triangle of an matrix as the example.

```

import tvm

from tvm import te

import numpy as np

import d2ltvm

```

In NumPy, we can easily use np.tril to obtain the lower triangle.

```

a = np.arange(12, dtype='float32').reshape((3, 4))

np.tril(a)

```

```

array([[ 0., 0., 0., 0.],

[ 4., 5., 0., 0.],

[ 8., 9., 10., 0.]], dtype=float32)

```

Now let's implement it in TVM with if\_then\_else. It accepts three arguments, the first one is the condition, if true returning the second argument, otherwise returning the third one.

```

n, m = te.var('n'), te.var('m')

A = te.placeholder((n, m))

B = te.compute(A.shape, lambda i, j: te.if_then_else(i >= j, A[i,j], 0.0))

```

Verify the results.

```

b = tvm.nd.array(np.empty_like(a))

s = te.create_schedule(B.op)

print(tvm.lower(s, [A, B], simple_mode=True))

mod = tvm.build(s, [A, B])

mod(tvm.nd.array(a), b)

b

```

#### 2.5.1 Summary

• We can use tvm.if\_then\_else for the if-then-else statement.

## 2.6 Truth Value Testing: all and any

In Python, we can use all and any to get the boolean return of a list of values. all returns the logical and result while any returns the logical or result.

```

import numpy as np

import d2ltvm

import tvm

from tvm import te

any((0, 1, 2)), all((0, 1, 2))

```

#### (True, False)

$\begin{bmatrix} 0 & 1 & 1 & 1 & 1 & 0 & 0 \end{bmatrix}$  $\begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}$

TVM provides similar te.all and te.any, which are useful to construct complex conditional expression for te.if\_then\_else.

The example we will use is padding the matrix a with 0s.

```

a = np.ones((3, 4), dtype='float32')

# applying a zero padding of size 1 to a

b = np.zeros((5, 6), dtype='float32')

b[1:-1,1:-1] = a

print(b)

[[0. 0. 0. 0. 0. 0.]

[0. 1. 1. 1. 1. 0.]

[0. 1. 1. 1. 1. 0.]

```

Now let's implement it in TVM. Note that we pass the four condition values into tvm.any.

Verify the results.

```

s = te.create_schedule(B.op)

mod = tvm.build(s, [A, B])

c = tvm.nd.array(np.empty_like(b))

mod(tvm.nd.array(a), c)

print(c)

```

```

[[0. 0. 0. 0. 0. 0.]

[0. 1. 1. 1. 1. 0.]

[0. 1. 1. 1. 1. 0.]

[0. 1. 1. 1. 1. 0.]

[0. 0. 0. 0. 0. 0.]]

```

### 2.6.1 Summary

• We can use tvm.any and tvm.all to construct complex conditional expressions.

# **3** Common Operators

In last chapter, we went over how to implement the basic expressions/operators using tvm operators. This chapter will further describe how to implement the typical operators we will encounter in the deep learning models.

# 3.1 Broadcast Add

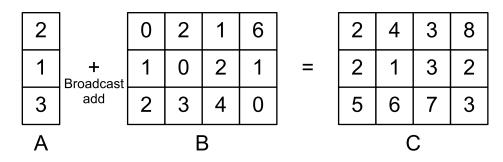

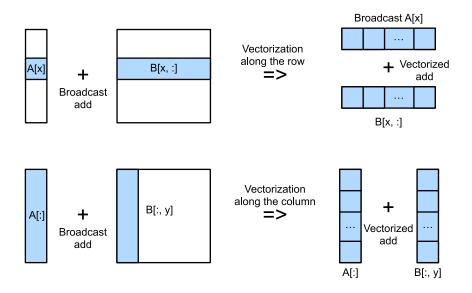

A broadcast operator process two tensors in different shapes. Normally, one of the operands has a particular dimension to be 1, which will be broadcast along the corresponding dimension of the other operator to perform the given calculation. Common scalar calculations can all be broadcast, such as elementary arithmetic and logical operations. Fig. 3.1.1 illustrates one broadcast add case between two 2-dimensional tensors. Broadcast operators are commonly seen in deep learning workloads, e.g. batch normalization<sup>15</sup>.

Fig. 3.1.1: One case of broadcast add between two 2-dimensional tensors

In this section we will demonstrate how to perform a broadcast add between two 2-dimensional tensors. The following code defines the computation.

```

import numpy as np

import tvm

from tvm import te

# Save to the d2ltvm package.

def broadcast_add(shape1, shape2):

"""Broadcast add between two 2-dimensional tensors

shape1, shape2 : the shapes of the input tensors

"""

```

(continues on next page)

<sup>15</sup> http://d2l.ai/chapter\_convolutional-modern/batch-norm.html

```

assert len(shape1) == 2 and len(shape2) == 2, \

"broadcast tensors should both be 2-dimension"

for i in range(len(shape1)):

assert shape1[i] == shape2[i] or shape1[i] == 1 or shape2[i] == 1, \

"tensor shapes do not fit for broadcasting"

A = te.placeholder(shape1, name='A')

B = te.placeholder(shape2, name='B')

m = shape1[0] if shape2[0] == 1 else shape2[0]

n = shape1[1] if shape2[1] == 1 else shape2[1]

f = lambda x, y: A[0 if shape1[0]==1 else x, 0 if shape1[1]==1 else y] + \

B[0 if shape2[0]==1 else x, 0 if shape2[1]==1 else y]

C = te.compute((m, n), f, name='C')

return A, B, C

```

Then we use it to perform the broadcast add illustrated in Fig. 3.1.1.

```

m = 3

n = 4

shape1 = (m, 1)

shape2 = (m, n)

A, B, C = broadcast_add(shape1, shape2)

s = te.create_schedule(C.op)

print(tvm.lower(s, [A, B], simple_mode=True))

mod = tvm.build(s, [A, B, C])

```

```

// attr [C] storage_scope = "global"

allocate C[float32 * 12]

produce C {

for (x, 0, 3) {

for (y, 0, 4) {

C[((x*4) + y)] = (A[x] + B[((x*4) + y)])

}

}

}

```

The printed pseudocode clearly depicts the process of a broadcast add. We verify the results as follows.

Note that broadcast is allowed to perform along multiple dimensions.

(3, 1) (1, 4) (3, 4)

Lastly, it is easy to note that when the shapes of two input tensors are indentical, the broadcast add reduces to an element-wise add.

### 3.1.1 Summary

- We can define a broadcast operator in TVM.

- Broadcast be can performed along multiple dimensions.

EE Exercise - Generalize broadcast\_add defined above to more dimensions and more operators.

## 3.2 Matrix Multiplication

Matrix Multiplication is one of the most widely operators in scientific computing and deep learning, which is typically referred to as *GEMM* (GEneral Matrix Multiply). Let's implement its computation in this section.

Given  $A \in \mathbb{R}^{n \times l}$ , and  $B \in \mathbb{R}^{l \times m}$ , if C = AB then  $C \in \mathbb{R}^{n \times m}$  and

$$C_{i,j} = \sum_{k=1}^{l} A_{i,k} B_{k,j}.$$

(3.2.1)

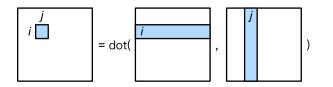

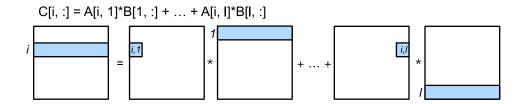

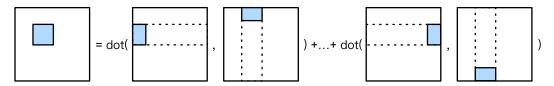

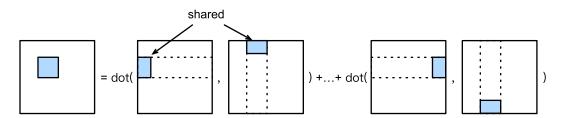

The elements accessed to compute  $C_{i,j}$  are illustrated in Fig. 3.2.1.

Fig. 3.2.1: Compute  $C_{x,y}$  in matrix multiplication.

The following method returns the computing expression of matrix multiplication.

```

import d2ltvm

import numpy as np

import tvm

from tvm import te

# Save to the d2ltvm package

def matmul(n, m, l):

"""Return the computing expression of matrix multiplication

A : n x l matrix

B : l x m matrix

C : n \times m matrix with C = A B

......

k = te.reduce_axis((0, 1), name='k')

A = te.placeholder((n, l), name='A')

B = te.placeholder((1, m), name='B')

C = te.compute((n, m)),

lambda x, y: te.sum(A[x, k] * B[k, y], axis=k),

name = 'C')

return A, B, C

```

Let's compile a module for a square matrix multiplication.

```

n = 100

A, B, C = matmul(n, n, n)

s = te.create_schedule(C.op)

print(tvm.lower(s, [A, B], simple_mode=True))

mod = tvm.build(s, [A, B, C])

```

```

// attr [C] storage_scope = "global"

allocate C[float32 * 10000]

produce C {

for (x, 0, 100) {

for (y, 0, 100) {

C[((x*100) + y)] = 0f

for (k, 0, 100) {

C[((x*100) + y)] = (C[((x*100) + y)] + (A[((x*100) + k)]*B[((k*100) +_-

·_y)]))

}

}

}

}

```

The pseudo code is simply a naive 3-level nested for loop to calculate the matrix multiplication.

And then we verify the results. Note that NumPy may use multi-threading to accelerate its computing, which may result in slightly different results due to the numerical error. There we use <code>assert\_allclose</code> with a relative large tolerant error to test the correctness.

### 3.2.1 Summary

- We can express the computation of matrix multiplication in TVM in one line of code.

- The naive matrix multiplication is a 3-level nested for loop.

# 3.3 Convolution

The convolution (*CONV*) operator is the one of the most expensive and popular operators in neural networks. In this section, we will cover the operator with single input and output channels. Please refer to chapter  $6.2^{16}$ ,  $6.3^{17}$ , and  $6.4^{18}$  in D2L for more explanation about this operator. Here we would not explain much about the convolution-related terms such as padding, channel, stride, convolution kernel, etc.

```

import d2ltvm

import numpy as np

import tvm

from tvm import te

```

### 3.3.1 Padding

As a prerequisite to convolution, let's first implement *padding*, which visually surrounds the targeting tensor with a "shell" surrounding it. The padding values are normally 0. Note that we briefly touched padding in Section 2.6 when introducing te.any, which was a padding for a 2-D matrix. Here we generalize the padding to work for 2-D convolution on *n*-D tensors, which is usually used in the convolution operators of neural networks. In the general case, we assume the last two dimensions are rows and columns, 0s are only padded on these two dimensions. In particular, if the matrix height (i.e. number of rows) is  $n_h$  and width (i.e. number of columns) is  $n_w$ , then we will pad  $p_h$  rows with 0s on top and bottom, and  $p_w$  columns with 0s on left and right to make its height and width to  $n_h + 2p_h$  and  $n_w + 2p_w$ , respectively. We have mentioned it once in Section 2.2, but again note that \*X and \*i in te.compute are used to represent general multi-dimensional tensors.

```

# Save to the d2ltvm package.

def padding(X, ph, pw, val=0):

"""Pad X with the given value in 2-D

ph, pw : height and width padding

val : padding value, default 0

"""

assert len(X.shape) >= 2

nh, nw = X.shape[-2], X.shape[-1]

return te.compute(

(*X.shape[0:-2], nh+ph*2, nw+pw*2),

lambda *i: te.if_then_else(

te.any(i[-2]<ph, i[-2]>=nh+ph, i[-1]<pw, i[-1]>=nw+pw),

val, X[i[:-2]+(i[-2]-ph, i[-1]-pw)]),

name='PaddedX')

```

Verify the results for a 3-D tensor.

<sup>&</sup>lt;sup>16</sup> http://numpy.d2l.ai/chapter\_convolutional-neural-networks/conv-layer.html

<sup>&</sup>lt;sup>17</sup> http://numpy.d2l.ai/chapter\_convolutional-neural-networks/padding-and-strides.html

<sup>&</sup>lt;sup>18</sup> http://numpy.d2l.ai/chapter\_convolutional-neural-networks/channels.html

```

A = te.placeholder((2,3,4))

B = padding(A, 1, 2)

s = te.create_schedule(B.op)

mod = tvm.build(s, [A, B])

a = tvm.nd.array(np.ones((2,3,4), dtype='float32'))

b = tvm.nd.array(np.empty((2,5,8), dtype='float32'))

mod(a, b)

print(b)

[[[0. 0. 1. 1. 1. 1. 0. 0.]

[0. 0. 1. 1. 1. 1. 0. 0.]

[0. 0. 1. 1. 1. 1. 0. 0.]

[0. 0. 1. 1. 1. 1. 0. 0.]

[0. 0. 0. 0. 0. 0. 0. 0. 0.]]

```

### 3.3.2 Convolution

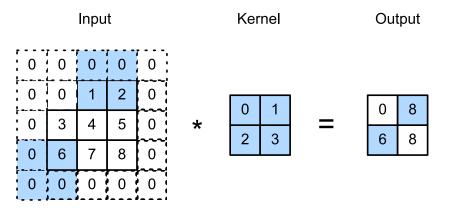

We consider the simple single-channel convolution first. Given an  $n_h \times n_w$  data matrix X, we first pad 0s into  $(n_h + 2p_h) \times (n_w + 2p_w)$ . If the kernel matrix K has a size of  $k_h \times k_w$ , using a stride  $s_h$  for height and  $s_w$  for width, the output  $Y = X \star K$  will have a shape

$$\lfloor (n_h - k_h + 2p_h)/s_h + 1 \rfloor \times \lfloor (n_w - k_w + 2p_w)/s_w + 1 \rfloor.$$

(3.3.1)

And the element of Y can be computed  $Y_{i,j}$  by

$$Y_{i,j} = \sum_{a=0}^{k_w - 1} \sum_{b=0}^{k_h - 1} X_{is_w + a, js_h + b} K_{a,b}$$

(3.3.2)

An example is illustrated in Fig. 3.3.1.

Fig. 3.3.1: The 2-D convolution with paddings for 1, and strides of 3 and 2 for height and width respectively. The shaded portions depicts the two output elements, with the corresponding input and kernel array elements used to calculate them:  $0 \times 0 + 0 \times 1 + 1 \times 2 + 2 \times 3 = 8$ ,  $0 \times 0 + 6 \times 1 + 0 \times 2 + 0 \times 3 = 6$ .

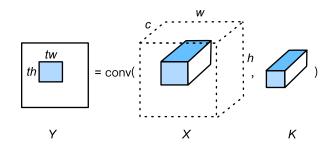

Now let's look at a more general case with multiple channels. Assuming that we have a  $c_i \times n_h \times n_w$  3-D input tensor X, and a  $c_o \times c_i \times k_h \times k_w$  4-D kernel tensor K, here  $c_i$  and  $c_o$  are the numbers of input channels and output channels, respectively. Then the output Y has a shape

$$c_o \times \lfloor (h - k_h + 2p_h)/s_h + 1 \rfloor \times \lfloor (w - k_w + 2p_w)/s_w + 1 \rfloor.$$

(3.3.3)

In particular, the *i*-th 2-D matrix  $Y_i$ ,  $i = 1, ..., c_o$ , is computed by

$$Y_{i} = \sum_{j=1}^{n} X_{j} \star K_{i,j}, \qquad (3.3.4)$$

where  $K_{i,j}$  is the 2-D kernel matrix with output channel *i* and input channel *j*.

In deep learning workloads, especially training, we often concatenate multiple inputs into a batch to process together. A batch of inputs has the shape  $n \times c_i \times n_h \times n_w$ , where n is the batch size. Applying convolution to a batch means running convolution on the n 3-D tensors separately, and then concatenates results into a 4-D tensor with the first dimension size being n.

Note that the input layout we used here is called NCHW, which means the 4 dimensions of the input tensors are batch, channel, height and width, respectively. conventionally, NCHW means the data is arranged in the memory with N being the outer most dimension and W being the inner most dimension. Sometimes we use other data layouts such as NHWC which may offer a higher performance. We will discuss this in detail later. Similarly, the kernel layout is defined as KCRS, which correspond to output channel, input channel, kernel height and width.

Before implementing the convolution, we define a method to calculate the output width or height given the input width or height.

```

# Save to the d2ltvm package.

def conv_out_size(n, k, p, s):

"""Compute the output size by given input size n (width or height),

kernel size k, padding p, and stride s

Return output size (width or height)

"""

return (n - k + 2 * p)//s + 1

```

Now let's implement the convolution. For simplicity we only consider the single batch case, i.e. N=1. In this case, the input data layout can be treated as CHW.

```

# Save to the d2ltvm package.

def conv(oc, ic, nh, nw, kh, kw, ph=0, pw=0, sh=1, sw=1):

"""Convolution

oc, ic : output and input channels

nh, nw : input width and height

kh, kw : kernel width and height

ph, pw : height and width padding sizes, default 0

sh, sw : height and width strides, default 1

.....

# reduction axes

ric = te.reduce_axis((0, ic), name='ric')

rkh = te.reduce_axis((0, kh), name='rkh')

rkw = te.reduce_axis((0, kw), name='rkw')

# output height and width

oh = conv_out_size(nh, kh, ph, sh)

ow = conv_out_size(nw, kw, pw, sw)

```

```

# pad X and then compute Y

X = te.placeholder((ic, nh, nw), name='X')

K = te.placeholder((oc, ic, kh, kw), name='K')

PaddedX = padding(X, ph, pw) if ph * pw != 0 else X

Y = te.compute(

(oc, oh, ow),

lambda c, i, j: te.sum(

PaddedX[ric, i*sh+rkh, j*sw+rkw] * K[c, ric, rkh, rkw],

axis=[ric, rkh, rkw]), name='Y')

return X, K, Y, PaddedX

```

Just as what we created get\_abc in Section 1.2, we define a method to get the input and output tensors. Again, we fix the random seed so it returns the same results if calling multiple times.

```

def get_conv_data(oc, ic, n, k, p=0, s=1, constructor=None):

"""Return random 3-D data tensor, 3-D kernel tenor and empty 3-D output

tensor with the shapes specified by input arguments.

oc, ic : output and input channels

n : input width and height

k : kernel width and height

p : padding size, default 0

s : stride, default 1

constructor : user-defined tensor constructor

.....

np.random.seed(0)

data = np.random.normal(size=(ic, n, n)).astype('float32')

weight = np.random.normal(size=(oc, ic, k, k)).astype('float32')

on = conv_out_size(n, k, p, s)

out = np.empty((oc, on, on), dtype='float32')

if constructor:

data, weight, out = (constructor(x) for x in [data, weight, out])

return data, weight, out

```

Now compile a module and compute the results.

```

oc, ic, n, k, p, s = 4, 6, 12, 3, 1, 1

X, K, Y, _ = conv(oc, ic, n, n, k, k, p, p, s, s)

sch = te.create_schedule(Y.op)

mod = tvm.build(sch, [X, K, Y])

print(tvm.lower(sch, [X, K, Y], simple_mode=True))

data, weight, out = get_conv_data(oc, ic, n, k, p, s, tvm.nd.array)

mod(data, weight, out)

// attr [PaddedX] storage_scope = "global"

allocate PaddedX[float32 * 1176]

produce PaddedX {

for (i0, 0, 6) {

for (i1, 0, 14) {

for (i2, 0, 14) {

PaddedX[(((i0*196) + (i1*14)) + i2)] = tvm_if_then_else(((((i1 < 1)_

\rightarrow || (13 <= i1)) || (i2 < 1)) || (13 <= i2)), 0f, X[((((i0*144) + (i1*12)) +...)]

⇒i2) - 13)])

```

```

}

}

}

}

produce Y {

for (c, 0, 4) {

for (i, 0, 12) {

for (j, 0, 12) {

Y[(((c*144) + (i*12)) + j)] = 0f

for (ric, 0, 6) {

for (rkh, 0, 3) {

for (rkw, 0, 3) {

Y[(((c*144) + (i*12)) + j)] = (Y[(((c*144) + (i*12)) + j)] + ...

→ (PaddedX[(((((ric*196) + (i*14)) + (rkh*14)) + j) + rkw)]*K[((((c*54) +...

}

}

}

}

}

}

}

```

In the last code block we also print out the pseudo code of a 2-D convolution, which is a naive 6-level nested for loop.

Since NumPy only has a convolution for vectors, we use MXNet's convolution operator as the ground truth. The following code block defines the data generating function and a wrap function to call the convolution operator. Then we can feed the same tensors to compute the results in MXNet.

Lastly, let's compare the results. For a similar reason mentioned in the last chapter, the multi-threading used in MXNet makes us use a relative large tolerant error here.

np.testing.assert\_allclose(out\_mx[0].asnumpy(), out.asnumpy(), atol=1e-5)

### 3.3.3 Summary

- We can express the computation of 2-D convolution in TVM in a fairly easy way.

- Deep learning workloads normally operate 2-D convolution on 4-D data tensors and kernel tensors.

- The naive 2-D convolution is a 6-level nested for loop.

# 3.4 Depthwise Convolution

Depthwise convolution is a special kind of convolution commonly used in convolutional neural networks designed for mobile and embedded applications, e.g. MobileNet (Howard et al., 2017).

```

import d2ltvm

import numpy as np

import tvm

from tvm import te

```

## 3.4.1 Compute definition

Let's revisit the 2-D convolution described in Section 3.3 first. The 2-D convolution basically takes a 3-D data (note that for simplicity we set the batch size to be 1) in size (ic, ih, iw), convolves it with a 4-D kernel in size (oc, ic, kh, kw), and produces an output data in size (oc, oh, ow). During the convolution, some padding and stride may be applied.

For depthwise convolution, the convolution computation itself stays the same, as illustrated in Fig. 3.3.1. It differs from the normal 2-D convolution in the way of organizing the convolution. In order to generate an output data in size ( $\circ\circ$ ,  $\circ$ ,  $\circw$ ) from input data in size ( $i\circ$ , ih, iw), a two-stage computation is needed. First, we process the input data with  $i\circ$  kernels, each of which convolves with the corresponding channel, to produce an intermediate data in size ( $i\circ$ , oh, ow); then we perform the normal, but pointwise, 2-D convolution on the intermediate data in size ( $i\circ$ , oh, ow) using a 4-D kernel in size ( $o\circ$ ,  $i\circ$ , 1, 1) to produce the output data in size ( $o\circ$ , oh, ow), where padding=0 and stride=1.

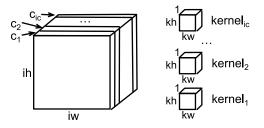

The computation of the second stage has been covered in Section 3.3. This section only focuses on the computation of the first stage, which is referred to as depthwise convolution. Fig. 3.4.1 illustrates its computation procedure.

From the figure we can see that the shape of the weight is a bit different from the 2-D convolution. The weight for depthwise convolution is 3-D, while it is 4-D for 2-D convolution. Therefore, we modify the

get\_conv\_data slightly to handle the generation of the data for depthwise convolution, and save it for future use.

```

# Save to the d2ltvm package.

def get_conv_data(oc, ic, n, k, p=0, s=1, constructor=None, conv_type='direct

→'):

"""Return random 3-D data tensor, 3-D kernel tenor and empty 3-D output

tensor with the shapes specified by input arguments.

oc, ic : output and input channels

n : input width and height

k : kernel width and height

p : padding size, default 0

s : stride, default 1

conv type: either direct 2D or depthwise, default direct

constructor : user-defined tensor constructor

.....

np.random.seed(0)

data = np.random.normal(size=(ic, n, n)).astype('float32')

ic_weight = ic

if conv_type == 'depthwise':

ic_weight = 1

weight = np.random.normal(size=(oc, ic_weight, k, k)).astype('float32')

on = d2ltvm.conv_out_size(n, k, p, s)

out = np.empty((oc, on, on), dtype='float32')

if constructor:

data, weight, out = (constructor(x) for x in [data, weight, out])

return data, weight, out

```

Comparing to Section 3.3, we added one argument to describe the convolution type, and make the input channel of the weight to be 1 when it is a depthwise convolution. You may wonder why we choose this dimension. The reason is to match the convention brought by the framework.

Then we define the depthwise convolution via TVM. Here, we reuse the padding and conv\_out\_size methods defined in Section 3.3.

```

from d2ltvm import padding, conv out size

# Save to the d2ltvm package.

def depthwise_conv(ic, nh, nw, kh, kw, ph=0, pw=0, sh=1, sw=1):

"""Convolution

ic : number of channels for both input and output

nh, nw : input width and height

kh, kw : kernel width and height

ph, pw : height and width padding sizes, default 0

sh, sw : height and width strides, default 1

.....

# reduction axes

rkh = te.reduce axis((0, kh), name='rkh')

rkw = te.reduce_axis((0, kw), name='rkw')

# output height and weights

oh = conv_out_size(nh, kh, ph, sh)

ow = conv_out_size(nw, kw, pw, sw)

# pad X and then compute Y

X = te.placeholder((ic, nh, nw), name='X')

```

```

K = te.placeholder((ic, 1, kh, kw), name='K')

PaddedX = padding(X, ph, pw) if ph * pw != 0 else X

Y = te.compute(

(ic, oh, ow),

lambda c, i, j: te.sum(

(PaddedX[c, i*sh+rkh, j*sw+rkw] * K[c, 0, rkh, rkw]),

axis=[rkh, rkw]), name='Y')

return X, K, Y, PaddedX

```

After defining the computation of depthwise convolution, we can use the default schedule to compile and execute it as follows. We also print out the pseudo-code of it.

```

ic, n, k, p, s = 256, 12, 3, 1, 1

X, K, Y, _ = depthwise_conv(ic, n, n, k, k, p, p, s, s)

sch = te.create_schedule(Y.op)

mod = tvm.build(sch, [X, K, Y])

print(tvm.lower(sch, [X, K, Y], simple_mode=True))

data, weight, out = get_conv_data(ic, ic, n, k, p, s,

constructor=tvm.nd.array,

conv_type='depthwise')

mod(data, weight, out)

// attr [PaddedX] storage_scope = "global"

allocate PaddedX[float32 * 50176]

produce PaddedX {

for (i0, 0, 256) {

for (i1, 0, 14) {

for (i2, 0, 14) {

PaddedX[(((i0*196) + (i1*14)) + i2)] = tvm_if_then_else(((((i1 < 1)_</pre>

\rightarrow || (13 <= i1)) || (i2 < 1)) || (13 <= i2)), 0f, X[((((i0*144) + (i1*12)) +...)

→i2) - 13)])

}

}

}

}

produce Y {

for (c, 0, 256) {

for (i, 0, 12) {

for (j, 0, 12) {

Y[(((c*144) + (i*12)) + j)] = 0f

for (rkh, 0, 3) {

for (rkw, 0, 3) {

Y[(((c*144) + (i*12)) + j)] = (Y[(((c*144) + (i*12)) + j)]

→+ (PaddedX[(((((c*196) + (i*14)) + (rkh*14)) + j) + rkw)]*K[(((c*9) +_

→(rkh*3)) + rkw)]))

}

}

}

}

}

```

}

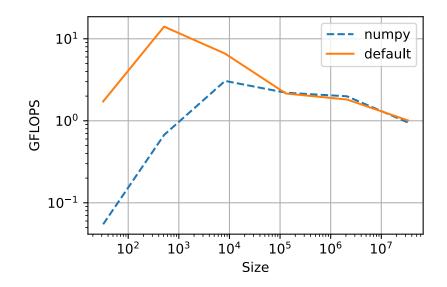

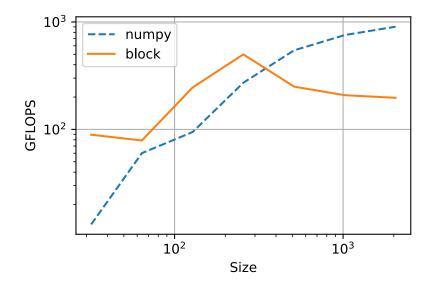

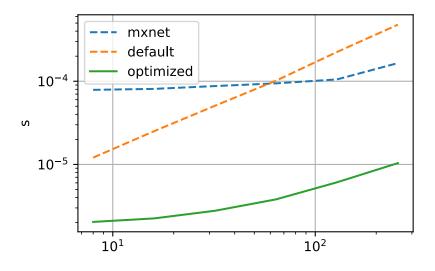

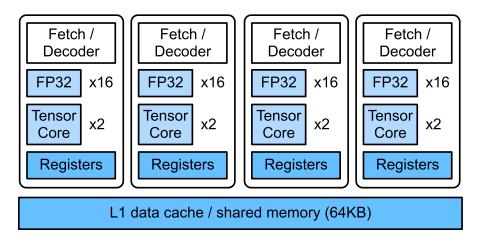

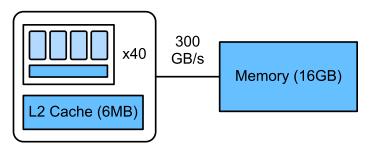

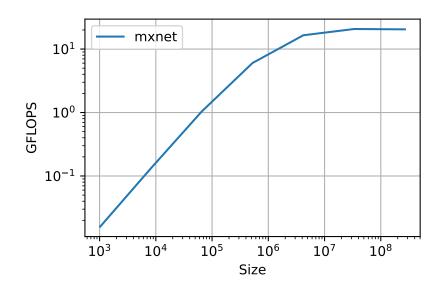

## 3.4.2 Depthwise Convolution in General